------♡ 서로 배려하는 물화생지 ♡------ (지우지 마세용)

1. 답변 달아주신 분께 감사의 댓글은 필수!

2. 모두 볼 수 있도록 비밀댓글은 금지!

3. 답변을 받은 후 질문글 삭제하지 않기!

4. 질문 전에 검색해보기! 질문은 구체적으로!

------♡ 서로 배려하는 물화생지 ♡------ (지우지 마세용)

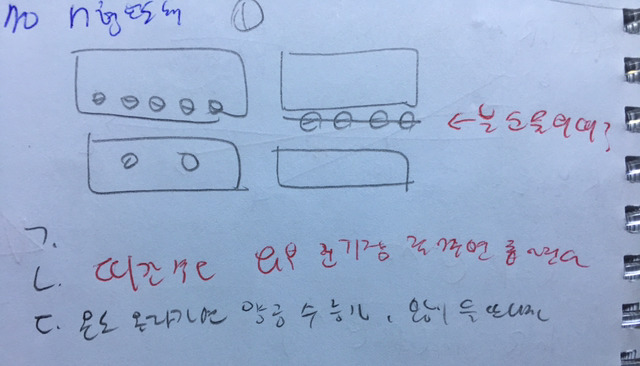

1. 반도체는 띠틈 에너지를 흡수해야 자유전자가 생길 수 있는데, 온도가 낮으면 띠틈 에너지를 흡수하는 전자의 수기 줄어들어 자유전자의 개수가 줄어들어 저항이 커진다 라고 하면 맞나요..?

2. N형 반도체에서 가전자 띠 아래에 오른쪽 그림처럼 선이 하나 더 나타나는 건 불순물의 띠인가요?

다음검색

댓글

댓글 리스트-

작성자고티카 작성시간 17.08.24 1. 띠틈 에너지를 흡수한다는 표현이 잘 이해가 되지 않네요. 설명을 더해주시면 감사하겠습니다.

2. N타입 반도체에서 가전자띠 아래 에너지 준위는 donor level 즉, 주개 준위 입니다. 불순물의 띠라고 생각해도 좋을거같네요. 더 상세한 내용을 알고싶으시면 페르미 준위와 화학퍼텐셜 같은 통계역학 개념을 공부하면 도움이 되겠네요. -

답댓글 작성자Shining 작성자 본인 여부 작성자 작성시간 17.08.24 1. 가전자띠와 전도띠 사이의 에너지 차이 = 띠틈 에너지 라고 표현 했어요.

답변 감사합니다 ^^ -

답댓글 작성자서울 물리 작성시간 17.09.19 P형 반도체에서는

에너지 준위가 어떻게 바뀌는지 아시나요?

N형에서는 저렇게

전도띠아래에 과잉전자들의 새로운 에너지준위가생겨서

전도띠로 오르기 쉽게되는데요.

P형반도체는 몰겠네요. -

답댓글 작성자고티카 작성시간 17.09.19 서울 물리 p형은 acceptor level을 valance level 가전자대에 형성해서 가전자대의 전자들이 살짝 들떠 가전자대에 양공이 생기게 됩니다~ 그래서 혼합된 페르미 준위가 낮아지는듯한 효과를 보이는 거에요

-

답댓글 작성자서울 물리 작성시간 17.09.19 고티카 감사합니다!