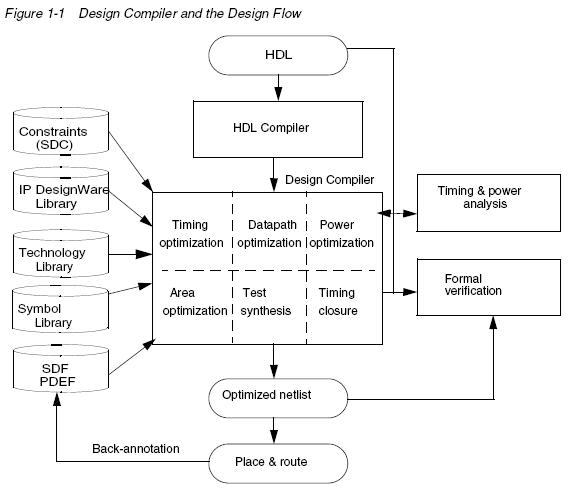

1. 디자인 컴파일러 소개

사용자 정의 게이트 어레이,FPGA,표준 셀 라이브러리를 사용하여

빠른(시간),면적 및 전력(Power) 효율적인 ASIC 칩을 만든다.

4가지 명령어

• Commands for Defining Design Rules(설계 규칙)

• Commands for Defining Design Environments(설계 환경) :loading,온도,전압 조건

• Commands for Setting Design Constraints(설계 제약)

• Commands for Analyzing and Resolving Design Problems(설계 문제 분석 및 해결)

1) Commands for Defining Design Rules(설계 규칙 명령어)

set_max_capacitance

Sets a maximum capacitance for the nets attached to the specified ports or to all the nets

in a design.

set_max_fanout

Sets the expected fanout load value for output ports.

set_max_transition

Sets a maximum transition time for the nets attached to the specified ports or to all the

nets in a design.

set_min_capacitance

Sets a minimum capacitance for the nets attached to the specified ports or to all the nets

in a design.

2) Commands for Defining Design Environments(설계 환경 명령어)

set_drive

Sets the drive value of input or inout ports. The set_drive command is superseded by

the set_driving_cell command.

set_driving_cell

Sets attributes on input or inout ports, specifying that a library cell or library pin drives the

ports. This command associates a library pin with an input port so that delay calculators

can accurately model the drive capability of an external driver.

set_fanout_load

Defines the external fanout load values on output ports.

set_load

Defines the external load values on input and output ports and nets.

set_operating_conditions

Defines the operating conditions for the current design.

set_wire_load_model

Sets the wire load model for the current design or for the specified ports. With this

command, you can specify the wire load model to use for the external net connected to

the output port.

3) Commands for Setting Design Constraints(설계 제약 명령어)

create_clock

Creates a clock object and defines its waveform in the current design.

set_clock_latency, set_clock_uncertainty, set_propagated_clock,

set_clock_transition

Sets clock attributes on clock objects or flip-flop clock pins.

set_input_delay

Sets input delay on pins or input ports relative to a clock signal.

set_max_area

Specifies the maximum area for the current design.

set_output_delay

Sets output delay on pins or output ports relative to a clock signal.

The advanced commands that set design constraints are

group_path

Groups a set of paths or endpoints for cost function calculation. This command is used to

create path groups, to add paths to existing groups, or to change the weight of existing

groups.

set_false_path

Marks paths between specified points as false. This command eliminates the selected

paths from timing analysis.

set_max_delay

Specifies a maximum delay target for selected paths in the current design.

set_min_delay

Specifies a minimum delay target for selected paths in the current design.

set_multicycle_path

Allows you to specify the time of a timing path to exceed the time of one clock signal.

4) Commands for Analyzing and Resolving Design Problems(설계 문제 분석 및 해결 명령어)

all_connected

Lists all fanouts on a net.

all_registers

Lists sequential elements or pins in a design.

check_design

Checks the internal representation of the current design for consistency and issues error

and warning messages as appropriate.

check_timing

Checks the timing attributes placed on the current design.

get_attribute

Reports the value of the specified attribute.

link

Locates the reference for each cell in the design.

report_area

Provides area information and statistics on the current design.

report_attribute

Lists the attributes and their values for the selected object. An object can be a cell, net,

pin, port, instance, or design.

report_cell

Lists the cells in the current design and their cell attributes.

report_clock

Displays clock-related information on the current design.

report_constraint

Lists the constraints on the current design and their cost, weight, and weighted cost.

report_delay_calculation

Reports the details of a delay arc calculation.

report_design

Displays the operating conditions, wire load model and mode, timing ranges, internal

input and output, and disabled timing arcs defined for the current design.