0739311 이경한

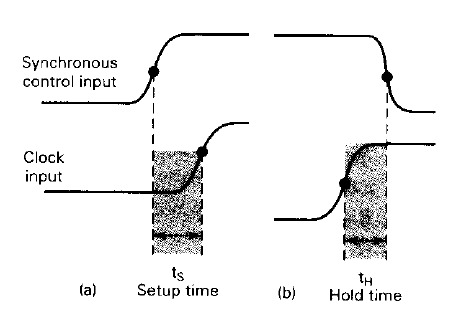

플립플롭의 안정 동작을 위한 타이밍 조건 : ts , th

- setup time, : ts

CLK의 에지 변화가 일어나기 전

입력의 레벨이 안정되어 있어야 하

는 최소시간

- hold time, : th

CLK의 에지 변화가 일어난 후 입

력이 일정 레벨로 유지되어야 하는

최소시간

ts - 는 5∼50 ns, th 는 0∼10 ns 범위

추가 적인 설명.

D flip-flop (DFF) 과 같은 동기 회로에서 안정적인 Input, Output 을 위해 필요한 일종의 딜레이를 말합니다.

DFF 의 예로 생각해 보자면, DFF는 Clock 의 rising edge 또는 falling edge 에서만 데이터를 읽는데,

이때 신호가 정확하게 0에서 1로 1에서 0으로 순간적으로 바뀌는게 아니다. 아래 그림처럼 어느정도 의 타이밍을 두고 liner 하게 변화하며 이때 데이터를 안정적으로 유지, 변환 해야 보장된 값을 얻을 수 있다.

이때 플립플롭이 읽혀지기 전에 Data 신호가 유효하도록 유지를 해야 하고, 읽혀지고 난 후,플립플롭이 변하는 동안 Data 신호가 유효하도록 유지를 해야할 필요성이 있는데 이 시간을 각각 Setup Time, Hold Time 이라 부른다. 이 두 딜레이로 Maximum Clock Frequency 등을 정할 수 있다.

setup time 과 hold time 에 대해 알아 보면,

setup time - clock 신호가 바뀌기 전까지 입력이 변화 없이 머물러 있어야 하는 시간

sampling 이 일어나기 전까지 입력이 올바로 인식 되는데 필요한 최소한의 시간 입니다

hold time - clock 신호가 바뀐 후에도 잠시 머물러 있어야 하는 시간

사건 발생 이후 올바로 입력이 인식 되기에 필요한 최소한의 시간 입니다