트랜지스터는 일반적인 접합 트랜지스터와 전계효과 트랜지스터로 구별한다는데

전계효과 트랜지스터라고 하는 것은 무엇일까?

전계효과 트랜지스터는 일반적인 트랜지스터와 마찬가지로 3개의 방향성 단자를 가지고 있고, 각각의 단자는 게이트(Gate),

드레인(Drain), 소스(Source)로 표기된다.

전계효과 트랜지스터란 Field Effect Transistor의 약자를 사용하여 FET라고 부르며, 일반적인 접합트랜지스터를

BJT(Bipolar Junction Transistor), 전계효과 트랜지스터를 Unipolar Transistor라고 부른다.

여기서 Unipolar란 단극성소자(單極性 素子, unipolar device)를 나타내며, (+) 또는 (-) 극성중 하나만을 가지고 있는 소자라고

이해하면 된다.

즉, 일반적인 트랜지스터의 동작 특성을 보면 정공과 전자에 의해 전류가 흐르는 것에 반해 전계효과 트랜지스터는 전자와 정공중

하나만으로 전류를 흐르게 하는 것이라고 이해하면 되고, 전류가 흐르는 통로를 채널(Channel)이라고 이해하면 된다.

따라서 전계효과 트랜지스터는 전류를 흐르게 할 채널을 P형 반도체와 N형 반도체중 어는 것을 사용하느냐에 따라 P채널

전계효과 트랜지스터와 N 채널 전계효과 트랜지스터로 구분되어진다.

이러한 전계효과 트랜지스터는 외부전원을 인가하는 게이트(Gate) 구조에 의해 접합형(J-FET)과 MOS 형 (MOS-FET)으로

크게 구별되는데, 입력 게이트가 반도체로 구성된 전계효과 트랜지스터를 접합 전계효과 트랜지스터(J-FET)라 하고,

입력 게이트가 산화 실리콘으로 절연되어있는 전계효과 트랜지스터를 MOS-FET라고 한다.

(J 는 Junction 을, MOS는 Metal Oxide Semiconductor 를 의미한다.)

그럼 J-FET와 MOS-FET에 대해 알아보자

J-FET

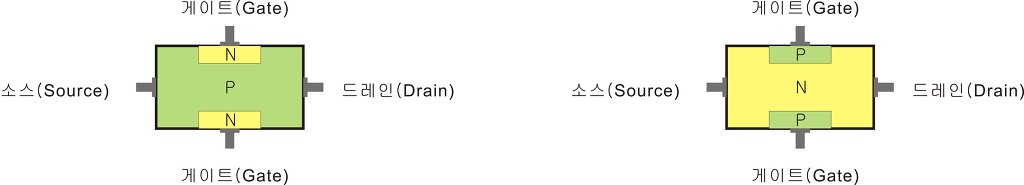

J-FET는 그림에서 보는 것과 같이 N형 반도체(또는 P형 반도체)의 양옆에 P형 불순물(또는 N형 불순물) 을 도핑하여 PN접합을

형성한 구조로 되어 있다.

J-FET 구조

P 채널 J-FET 구조 N 채널 J-FET 구조

이러한 반도체의 양단은 저항성 접촉 전극으로 연결되어 있고, 이 전극 사이에 전압을 인가하면 채널에 전류가 흐르게 된다.

N 채널의 경우 전류가 흘러 들어가는 방향이 드레인(Drain), 전류가 흘러 나오는 방향이 소스(Source)이므로

소스 단자는 (-), 드래인 단자는 (+) 전압이 인가되어야 하고,

P 채널의 경우 전류가 흘러 들어가는 방향이 소스(Source), 전류가 흘러 나오는 방향이 드레인(Drain)이므로

소스 단자는 (+), 드래인 단자는 (-) 전압이 인가되어야 한다.

(그림에서 2개의 게이트(Gate) 펼친 그림 때문에 2개로 표시 되었으나 실제는 1개로 구성된다.)

또 J-FET 는 어떻게 동작하는 것일까?

J-FET은 게이트와 소스사이에 역방향 전압(게이트 전압)을 공급하여 드레인과 소스 사이에 흐르는 드레인 전류의 흐름을

제어하게 된다.

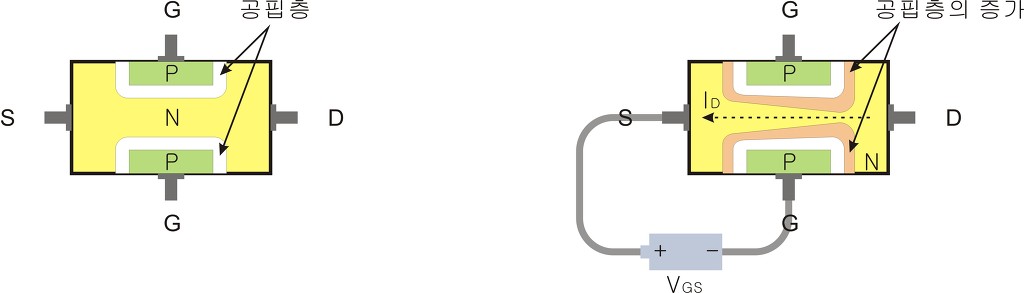

채널 반도체에 도핑된 불순물은 PN 접합형태가 되고, 공급되는 게이트 전압에 의해 PN 접합면에 공핍층 형성이 감소, 증가되어

채널 반도체에 전류가 흐를 수 있는 폭이 감소 또는 증가하게된다.

공핍층의 형성과 게이트 전압에 의한 공핍층의 증가

다시말해서, 게이트에 공급되는 역방향 전압에 의해 공핍층이 많이 생기게 되면 전류가 통과할 수 있는 채널이 좁아지게 되고,

전류 흐름이 감소하게 되는데, 궁극적으로 게이트 전압을 계속 올리게 되면 공핍층이 점점 넓어져 결국 채널이 막히는 현상이

나타나게 되는데 이러한 현상을 Pinch-off , 쉽게 표현해서 FET가 포화되었다라고 할 수 있다.

이때의 게이트와 소스 전압을 Pinch-off 전압이라고 한다.

이렇듯 J-FET는 게이트 전압에 의해 드레인과 소스사이의 전류를 제어할 수 있게 되는 것이다.

(여기서 공핍층이란 PN 접합 반도체의 접합면에 생성되는 영역으로 전자 또는 정공이 존재하지 않는 영역을 말하는데,

전자나 전공이 존재하지 않으면 전류가 흐를 수 없게 된다. 이러한 공핍층을 공간전하층이라고도 한다.)

J-FET 게이트 전압 공급과 전류흐름

P 채널 J-FET N 채널 J-FET

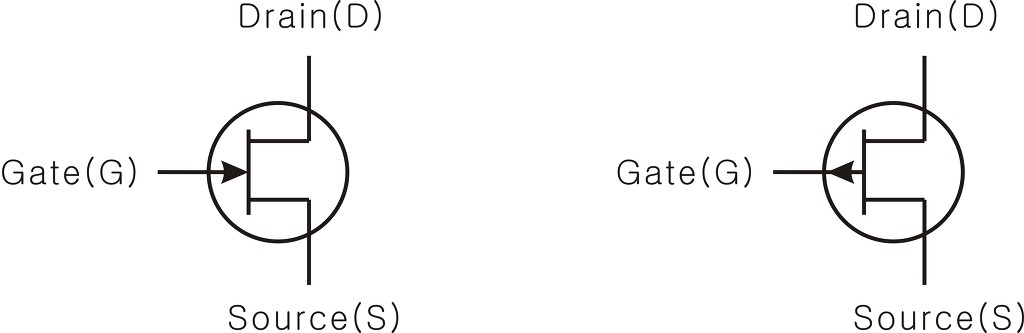

이렇듯 J-FET는 게이트 전압에 의해 드레인과 소스사이의 전류를 제어할 수 있게 되는 것으로 심볼은 게이트 전압에 걸리는

전압의 방향성 화살표시를 그림과 같이 표시한다.

게이트에 표시된 화살표시는 게이트 접합부의 순방향을 표시한 것으로 화살표가 바깥을 향하면 P 채널이고, 화살표가 안쪽으로

향하면 N 채널을 의미한다.

통상 J-FET는 P 채널형 보다는 N 채널형이 많이 쓰인다.

J-FET 심볼

N 채널 J-FET P 채널 J-FET