전원회로에 대해 알아봅시다 - 7 : 제어형 정전압회로

제어형 정전압회로에 대해 알아봅시다.

제어형 정전압회로는 트랜지스터를 사용한 정전압회로를 더욱 발전시킨 직렬형 정전압회로로, 출력단에 저항으로

구성된 분압회로를 이용하여 출력전압의 변화를 검출하고, 검출된 변화값을 궤환(Feedback) 시켜 출력전압을

안정시키는 구조로 되어있다고 하였습니다.

또한, 제어형 정전압회로는 출력단의 분압회로를 가변저항으로 구성하여여 출력전압을 가변할 수 있는 출력전압

가변형 정전압회로 또는 독립된 가변 전원공급기로 많이 사용된다고 하였답니다.

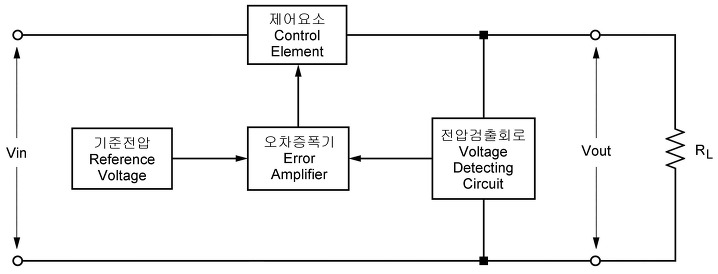

제어형 정전압회로의 블록 구성을 살펴보면 직렬형 정전압 회로를 개선하기 위해 다음과 같이 피드백 회로와

오차 증폭기(Error Amp: 또는 오차 검출기, 비교 증폭기)를 직렬 회로에 추가 하여 구성하게 되는데, 제어회로의

오차 증폭기는 트랜지스터 또는 연산증폭기(OP amp)를 사용한답니다.

제어형 정전압 회로의 블록 구성

트랜지스터 제어형 정전압회로에 대해 알아보겠습니다.

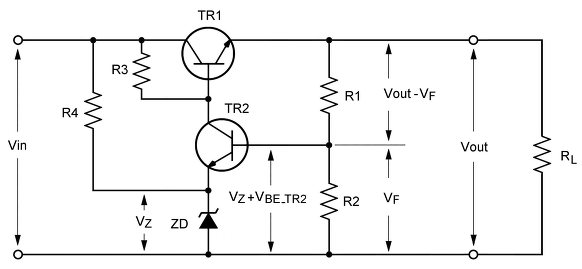

트랜지스터 제어형 정전압회로

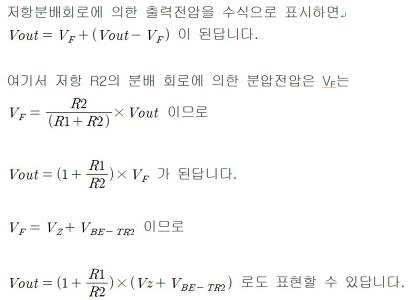

트랜지스터 제어형 정전압회로를 살펴보면 부하와 직렬로 연결된 제어요소로 TR1, 저항분배회로로 구성된

전압검출회로, 기준전압 생성을 위한 제너다이오드 ZD와 검출전압과 기준전압을 비교하는 오차증폭기 TR2로

구성되어 있답니다.

회로 동작은 입력된 전압이 R4 와 ZD에 의해 기준 전압 Vz가 만들어 지고, TR1을 통한 출력전압은

저항 분배회로에 의해 Vout-VF와 VF로 분압 된답니다.

여기서 분압된 VF 전압은 궤환되어 TR2의 베이스에 인가되고, TR2 부하저항 R3에 흐르는 전류의 변화에 의해

TR2 에미터에 연결된 제너다이오드 ZD의 기준 전압 Vz와 비교를 하게 된답니다.

출력전압 Vout이 높아지면 VF 전압도 높아지게 되는데, VF 전압이 TR2의 기준전압보다 높게 되므로,

부하저항 R3에 흐르는 전류는 증가하게 된답니다.

따라서 TR2 콜렉터 전류가 증가하게 되고, TR1의 베이스 전압이 낮아지게 되므로 TR1의 출력전압이 감소하게

된답니다.(아주 쉽게 말하면 에미터에 걸려있는 기준전압보다 큰 분압 이 베이스에 입력되면 TR2가 도통되어

TR1으로 흐를 수 있는 전류가 TR2로 흘러 버려 TR1에 흐르는 전류가 감소하게 되고, TR1을 통해 부하에 흐르는

전류가 감소하기 때문에 출력 전압이 낮아진다고 하는 것이랍니다.)

또한 출력전압 Vout이 낮아지면 VF 전압도 감소되고, TR2의 부하저항 R3에 흐르는 전류가 감소하게 되어

TR1 베이스 전압이 증가 되므로 TR1의 출력전압이 증가하게 된답니다.

이렇듯, 분압 VF가 기준전압 수준에 도달 할 때까지 트랜지스터 TR1의 출력상태를 제어함으로 출력 전류와 Vout은

증가 또는 감소하게 되어 출력전압은 일정한 레벨을 유지하게 되는 것이랍니다.

(저항에 의한 전압의 분배(분압)는 “부품에 대해 알아봅시다/저항이란?/저항연결방법을 이용한 전압과 전류의

분배(저항회로의 분압)"을 먼저 숙지하시면 쉽게 이해할 수 있답니다.)

계속해서 연산증폭기(OP AMP) 제어형 정전압회로에 대해 알아봅시다.

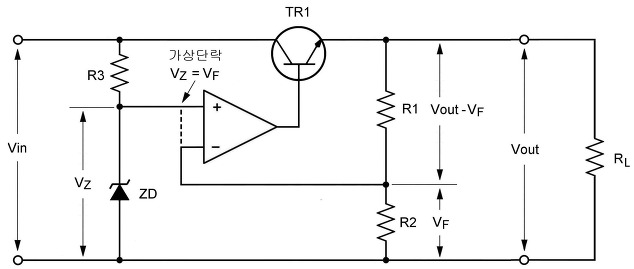

연산증폭기(OP AMP) 제어형 정전압회로

연산증폭기(OP AMP) 제어형 정전압회로를 살펴보면 부하와 직렬로 연결된 제어요소로 TR1, 저항분배회로로

구성된 전압검출회로, 기준전압 생성을 위한 제너다이오드 ZD와 검출전압과 기준전압을 비교하는 오차증폭기인

연산증폭기(OP AMP)로 구성되어 있답니다.(연산증폭기(OP AMP) 제어형 정전압회로는 트랜지스터 제어형

정전압 회로와 동일한 회로 구성을 가지고 있는데 제어용 트랜지스터가 연산증폭기(OP AMP)로 바뀌었고

연산증폭기(OP AMP)는 제너다이오드의 기준전압과 출력단의 분배 전압을 비교하는 비교기로 사용되었답니다.)

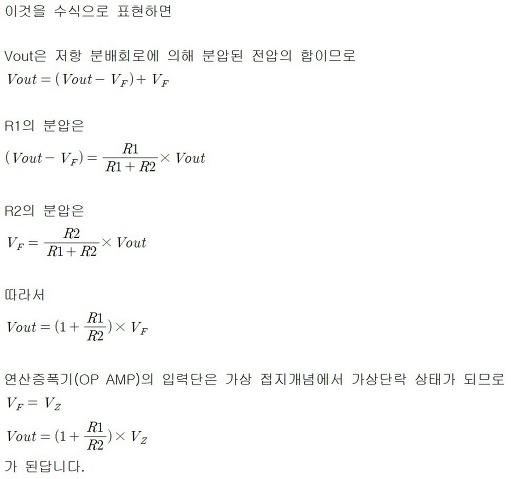

회로 동작은 입력된 전압이 R3 와 ZD에 의해 기준 전압 Vz가 만들어 지고, TR1을 거친 출력전압은 저항 분배회로에

의해 VF로 분압 된답니다.

분압된 VF는 연산증폭기(OP AMP)로 궤환되어 제너다이오드 ZD의 기준 전압 Vz와 비교를 하게 된답니다.

출력 트랜지스터 TR1은 연산증폭기(OP AMP)에 의해 구동되는데, 트랜지스터의 출력전압이 변하게 되면 출력단의

분배회로에 의한 분압 VF 역시 변하게 되고, 연산증폭기(OP AMP)로 궤환되어 기준전압 Vz와 비교되어진답니다.

여기서 연산증폭기(OP AMP)의 입력단은 가상 접지 개념의 가상단락 상태이므로 궤환된 분압 Vf와 제너다이오드의

기준전압 Vz는 같아야 된답니다.

따라서 출력전압이 변하게 되면 연산증폭기(OP AMP)의 기준전압과 궤환 분압 VF의 관계가 VF≠Vz이 되어

연산증폭기(OP AMP)는 전압 비교기(voltage Compatator)로 동작하게 되어 제어신호를 트랜지스터의 베이스로

보내게 되고, 트랜지스터의 출력상태를 제어하게 되므로 트랜지스터의 출력전압은 일정한 레벨을 유지하게

되는 것이랍니다.

다음은 전류제한 회로에 대해 알아보겠습니다.