기본 이론

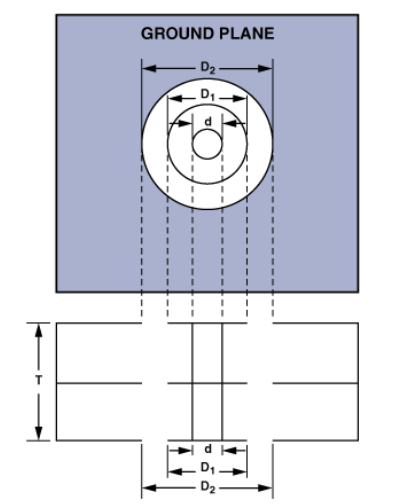

Via는 종종 Signal 배선의 한 부분이 된다. 보통 Via는 여러 Part 주변에서 배선을 간단하게, 혹은 고밀도 Interconnection등이 필요한 곳에서 PCB Layer간 수직 연결 통로 역할을 담당한다. PCB Trace와 함께, PCB Via 역시 관련 기생 커페시턴스, 인덕턴스, 임피던스를 가지게 된다. (물리적인 회로 구조에는 다 있는 것). 이 기생 값들은 보통 아래의 식과 같이 구해진다.

Capacitance : C = 1.41x E x T x D1/(D2-D1) ------------ (1)

Inductance : L = 5.08H x [ln(4H/D1)+1] ----------------- (2)

E = 유전상수, D1 = Via 직경, D2 = Via Anit-pad 직경, T = PCB 두께, H = Via 길이 (보통 PCB 두께)

-----> "High Speed Digital Design 교제에 잘 설명 되어 있으니 Via chapter 참조.

D1, D2, H, T는 모두 Inch 단위이므로 선택적으로 Dimension 변화해서 사용해야 하며, Via strucutre에 대해 아래 참조 하면 도움이 될 듯 하다. 이러한 식으로써 표현 한것은 보통 Via의 작은 치수 특성때문에 Lumped model로 본 실험식으로 보는 것이 옳은듯 하다.

이렇게 형성된 Capacitance와 Inductance는 Signal의 Rise/Fall time을 증가시켜, Time delay를 유발하게 된다. 저주파 에서는 효과가 미약하겠지만, High speed 설계에서는 꼼꼼히 따져봐야 될것이다.

Via는 보통 Trace routing 중에 형성되므로, Trace line Impedance에 영향을 준다. Via의 물리적 Dimension및 주변 회로 여건에 따라 다르겠지만, 일반적으로 10% 정도의 Impedance drop시키는 것으로 알려져 있다. 따라서 50Ohm trace에서 Reflection coefficient 는 5%로 볼 수 있다. [(50-45)/(50+45)]. 대부분의 High Speed design은 수 mA정도의 Carrying 전류를 가지므로 Via impedance의 영향은 Via capacitance 나 Inductance의 영향에 비해 미세하다.

Case Study - Design

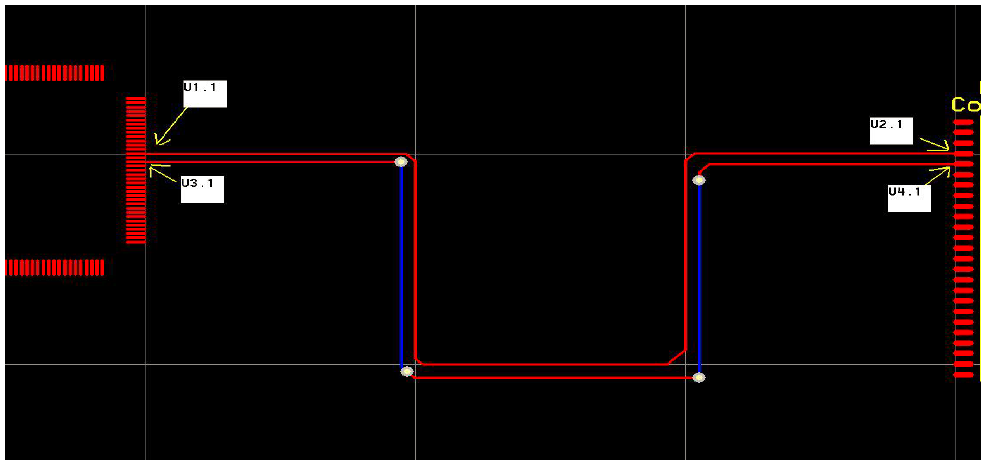

Via의 Signal Integrity 영향을 예측하기 위해, 4L PCB에 2 Micro Strip line을 구현하여 보았다.

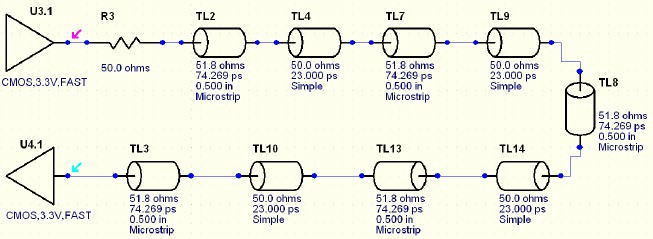

Net 1 : U1.1 과 U2.1간 2.5inch Micro Stripline으로 연결되어 있고, Characteristic impedance는 51.8 Ohm 이다.

U1.1에 50 Ohm Resistor가 직렬로 연결되어 Source termination 되어 있다.

Net2 : U3.1과 U4.1 사이에 0.5 Inch 씩 5개의 trace로 Net1과 동일한 길이로 설계하였으며, 4개의 10mil/20mil Via가 사용되었다.

Modeling

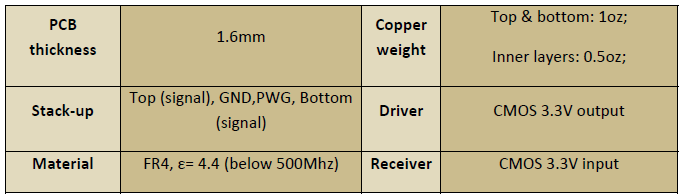

Simulation set up 및 PCB에 대한 정보는 상기 Table과 같고, Simulation을 위한 Net1 과 Net2의 Model은 아래와 같다.

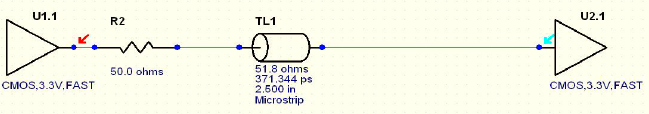

Net1 IBIS

Net2 IBIS

Analysis

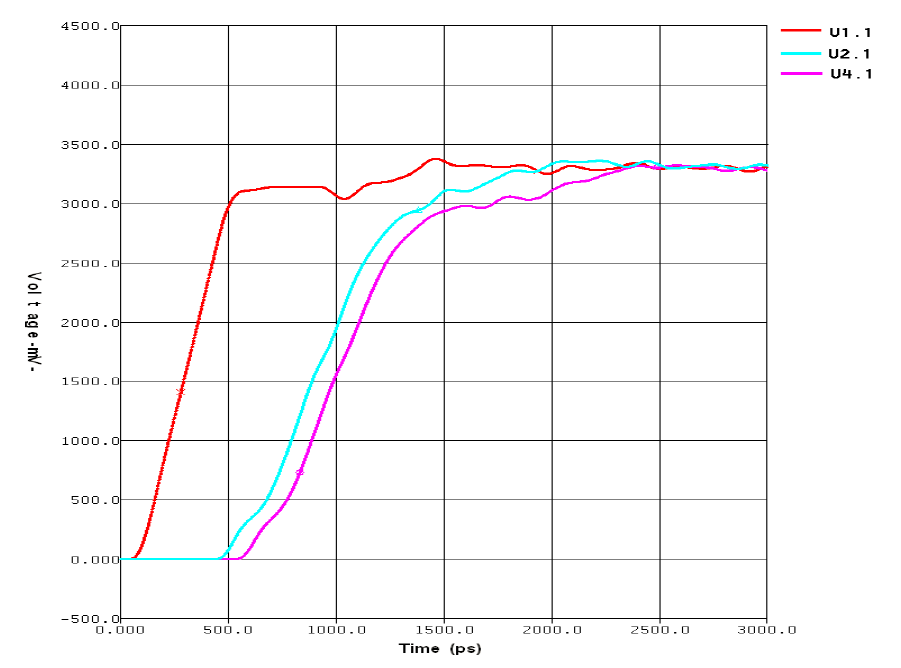

<Graph1 : Rising Edge Waveform>

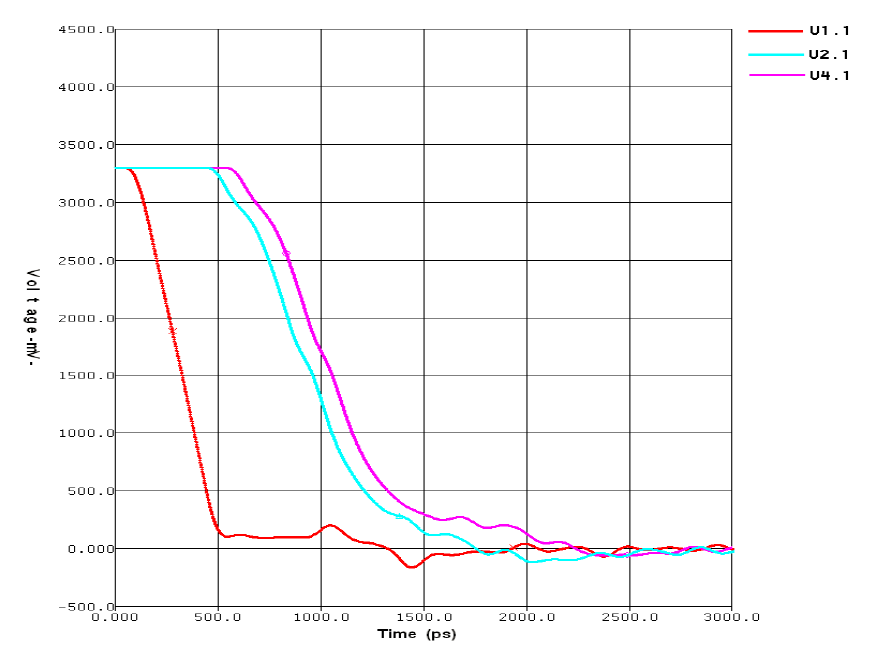

<Graph2 : Falling Edge Waveform>

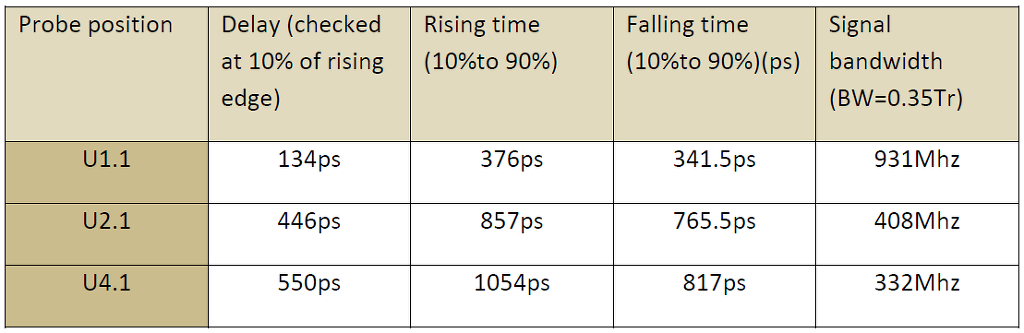

Simulation은 Mentor Graphics 의 Hyperlynx linesim 이 이용되었다. 주파수는 400Mh , Signal Skew는 Driver단에서

400ps이다. U1.1, U2.1 & U3.1, U4.1 핀에 High impedance probe를 이용하여 Time domain parameters 들을 분석

하였다. 위 Graph는 Rise and Fall Edge waveform을 표현하였다. 아울러 아래 table은 Time domain parameter 값이다.

TGraph1에서 볼 수 있듯이 U1.1 에서의 Rise time 보다 U2.1에서의 Rise time 이 줄어 들었고, 이는 트랜스 미션 line의

Parastic 때문이다. 동길이의 트랜스미션 line인 Net2의 Rise time은 더 줄었으며 이는 Via에 의한 영향으로 보여진다.

명백히, Trace에 있는 Via는 Signal wave form 에 나쁜 영향을 주는 것이다.

추가적으로 Via 가 주는 영향력을 분석하기 위해 서로 다른 Via 2,3,4로 (10/20 & 20/40 mils) Net2 를 시뮬레이션 하였고

그 결과는 아래와 같다.

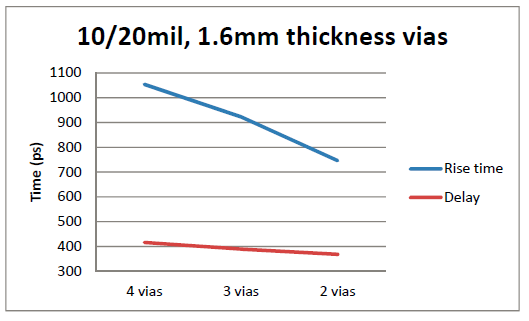

(10/20 mils Vias, 1.6mm thickness @U4.1)

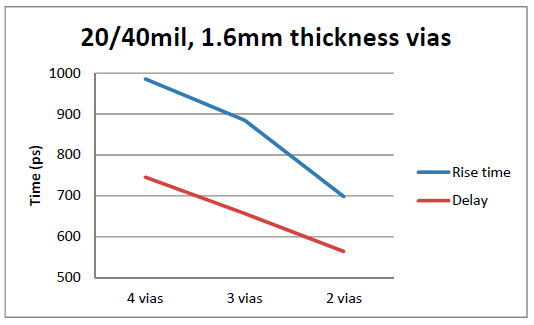

(20/40 mils vias, 1.6mm thickness @U4.1)

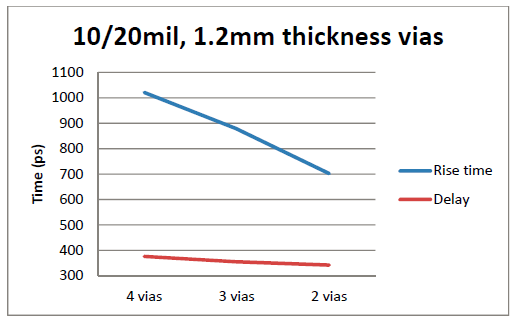

(10/20 mils vias, 1.2mm thickness @ U4.1)

위의 Graph에 해당하는 결과를 통해서 알 수 있는 것을 정리해 보면,

1. Via의 갯수가 적을 수록 Rise time과 Delay가 작다는 것을 알 수 있다.

2. Via size가 작을 수록, Delay가 작음을 알 수 있다. 하지만 Rise time 면에서는 영향이 미비하다.

3. Via length를 줄이면 작은 Delay와 빠른 Rise time을 얻을 수 있다.

이러한 단순한 결과들이 항상 옳지는 않으므로, 실제 Circuit의 Simulation등을 통해 정확도 높은 Simulation을 통해

해당 설계를 Verify하는 것이 가장 좋은 방법일 것이고, 실제 대부분의 기업에서는 이러한 Process를 운용하고 있다.

실용지침

아래 Via design guideline 몇가지를 사용하여 PCB 설계를 진행할 것을 추천하며, 이는 저가이면서 고성능, 안정성을

겸비한 PCB를 구현 할 수 있다.

High Speed Circuit에서

1. Signal distortion을 야기하는 Via의 사용과 Layer 변경을 가급적 줄여라. Pin to Pin간의 연결을 가급적 trace만을

이용하여 연결하면 좋고, 연결해야할 Pin이 다른 layer에 있다면 Via의 갯수를 Minimize하는 것이 좋다.

2. 특히 고주파 Clock line의 경우는 각별히 1. rule에 더 신경써서 routing하라.

3. 불필요한 Via pad를 줄여라. 이렇게 평행판의 형태를 가지는 Via pad는 Capacitance을 유발한다. 따라서 없앨 수

없는 경우라면 해당 Via pad 와 인접 layer에서 metal 이 겹치는 것을 최대한 줄여 Capacitance를 줄이는 것이 좋다.

4. 작은 Via가 적은 capacitance를 가지게 되고, 길이가 작고 Via diameter가 클수록 작은 Inductance를 가지게 되므로

실제 설계에서 유용하게 적용할 수 있다. 특히 Inductance의 control은 여러모로 회로에 좋지 않은 영향을 미치므로,

설계시 Inductance를 줄일려고 노력하는 know how를 키워라

5. 특히 differential pair의 경우 Via 갯수를 같이 하는 것이 중요하다. 앞서 본 시뮬레이션의 결과를 보게되면 많아진

Via의 갯수가 회로에서 어떤 영향을 미칠 것인지 짐작이 가리라 본다. Skew 나 Phase 차이등이 생기면 좋을게 없다.